In questo articolo studiamo i BUS nei sistemi di elaborazione e le loro funzioni

Sommario

Il bus di sistema e l’interazione tra CPU e RAM

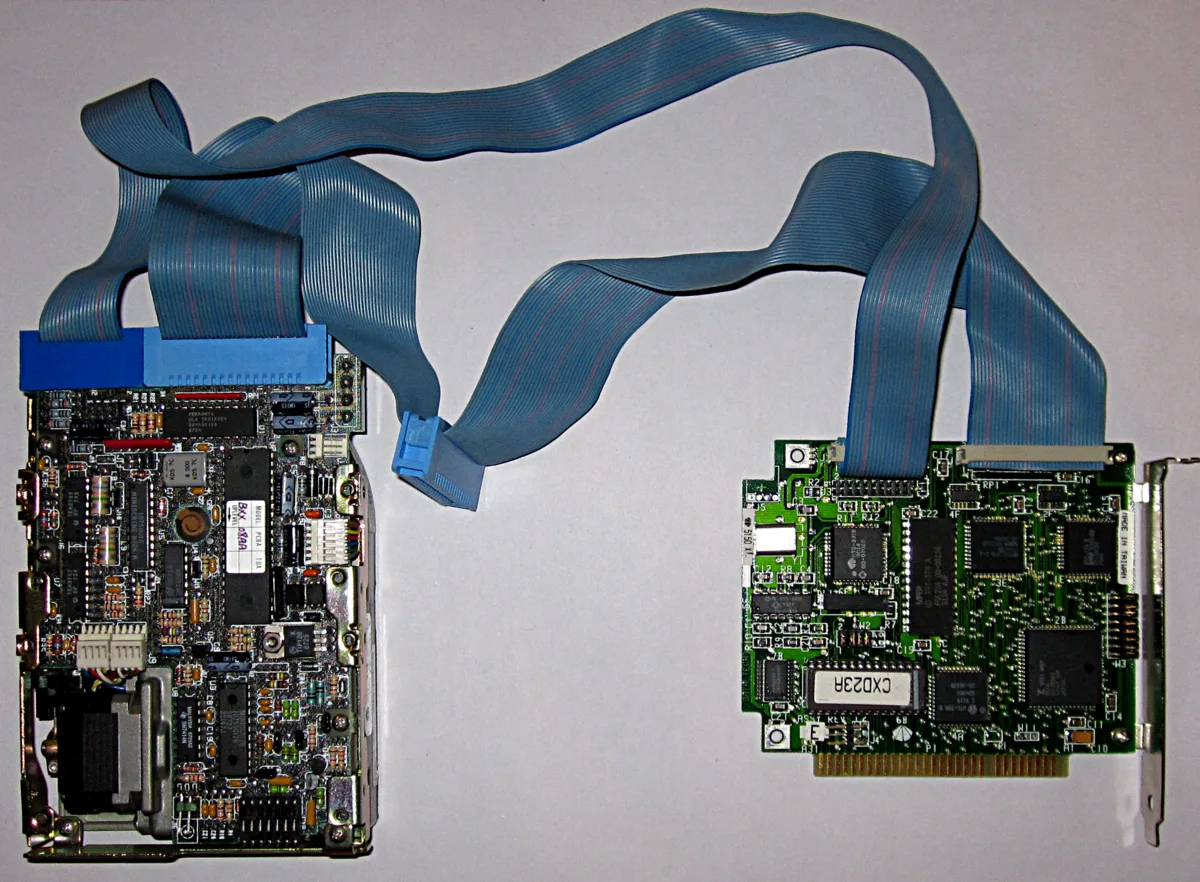

Le componenti fondamentali di un sistema di elaborazione – come la CPU, la memoria centrale e le periferiche – sono collegate tramite un insieme di linee elettriche chiamato bus di sistema (system bus). Questo complesso di collegamenti, disposto sulla scheda madre, permette il trasferimento di dati, indirizzi e segnali di controllo tra i vari dispositivi del computer.

Organizzazione del bus

Il bus di sistema è suddiviso in tre sottosistemi principali:

-

Bus dati (Data Bus):

Trasporta le informazioni (istruzioni e dati) tra la CPU, la memoria e le periferiche. È bidirezionale, poiché i dati possono fluire in entrambe le direzioni. Il numero di linee (fili) che lo compongono determina la larghezza del bus e influisce sulla quantità di dati trasferibili contemporaneamente. Ad esempio, un bus a 32 bit può trasferire 4 byte per operazione, mentre uno a 64 bit può trasferirne 8. -

Bus indirizzi (Address Bus):

Utilizzato dalla CPU per selezionare una specifica locazione di memoria o una periferica. È monodirezionale: la CPU invia l’indirizzo, ma non riceve informazioni tramite questo bus. Il numero di linee determina la quantità di indirizzi disponibili. Ad esempio, un bus indirizzi a 16 bit consente di indirizzare 2¹⁶ = 65.536 celle di memoria (64 KB). -

Bus di controllo (Control Bus):

Trasporta i segnali di controllo utilizzati per coordinare e sincronizzare le operazioni del sistema, come lettura (RD), scrittura (WR), abilitazione della memoria (MREQ) e il segnale di clock. Le linee di controllo possono essere unidirezionali o bidirezionali, ma ogni singola linea è unidirezionale.

Il ciclo macchina: lettura e scrittura in memoria

L’interazione tra la CPU e la memoria centrale (RAM) avviene mediante cicli di lettura e scrittura, sincronizzati dal segnale di clock del sistema. Questi cicli coinvolgono la gestione combinata dei tre bus sopra descritti.

Ciclo di lettura dalla memoria

- La CPU pone l’indirizzo della locazione di memoria sul bus indirizzi.

- Il segnale MREQ (Memory Request) viene attivato (a livello basso) per abilitare il chip di memoria.

- Il segnale RD (Read) viene attivato per indicare alla memoria che deve collocare il dato richiesto sul bus dati.

- La CPU legge il dato dal bus dati. Il segnale WR rimane disattivo (alto).

Ciclo di scrittura nella memoria

- L’indirizzo della locazione di memoria da modificare viene posto sul bus indirizzi.

- Il segnale MREQ viene attivato per selezionare il chip di memoria.

- Il dato da scrivere viene collocato sul bus dati.

- Il segnale WR (Write) viene attivato per indicare che la CPU desidera scrivere nella memoria. Il segnale RD rimane disattivo.

⚠️ Durante un’operazione di scrittura è essenziale che solo un dispositivo controlli il bus dati, per evitare conflitti.

Calcolo del tempo di trasferimento durante un ciclo di lettura

Durante una operazione di lettura, il tempo totale è dato dalla somma di tre componenti:

- t₁: tempo necessario a trasferire l’indirizzo della locazione di memoria (sul bus indirizzi)

- t₂: tempo di accesso della memoria, ovvero quanto tempo impiega il dato a diventare disponibile

- t₃: tempo necessario per trasferire il dato sul bus dati verso la CPU

Esempio pratico

Un bus sincrono ha le seguenti caratteristiche:

- Durata di un ciclo di clock: 25 ns

- Durata di una trasmissione sul bus: 2 cicli di clock (quindi 50 ns)

- Bus dati: 32 bit

- Bus indirizzi: 32 bit

- Memoria: tempo di ciclo pari a 100 ns

- Capacità di ogni locazione di memoria: 64 bit

La CPU deve leggere una locazione di memoria da 64 bit, ma il bus dati è largo 32 bit. Occorrono due trasferimenti.

Soluzione:

- t₁ = 50 ns (trasferimento indirizzo)

- t₂ = 100 ns (tempo di accesso della memoria)

- t₃ = 50 ns + 50 ns = 100 ns (trasferimento in due blocchi da 32 bit)

👉 Tempo totale:

t = t₁ + t₂ + t₃ = 50 ns + 100 ns + 100 ns = 250 ns

Lascia un commento